## OM6621Dx

Bluetooth Low Energy Compliant & 2.4-GHz Proprietary

System-on-Chip

V1.3

Datasheet

# **Table of Contents**

| Version History                   | 6   |

|-----------------------------------|-----|

| 1 OM6621Dx Overview               | 7   |

| 1.1 Description                   | 7   |

| 1.2 Features                      | 7   |

| 1.3 System Function Block Diagram | 8   |

| 1.4 Applications                  | 9   |

| 2 Pinout                          | 10  |

| 2.1 QFN20                         | 10  |

| 2.2 QFN32                         | 11  |

| 2.3 Pin Description               | 12  |

| 3 MCU Subsystem                   | 14  |

| 3.1 MCU Debug                     | 14  |

| 3.2 Interrupts Vector             | 14  |

| 3.3 Electrical Specifications     | 15  |

| 3.4 Module Address Mapping        |     |

| 4 Memory                          | 17  |

| 4.1 Memory Introduction           | 17  |

| 4.2 Memory Map                    | 17  |

| 4.3 APB Address Space             | 17  |

| 5 PMU                             | 19  |

| 5.1 Power Management              | 19  |

| 5.2 Digital LDO                   | 19  |

| 5.3 POR/BOD                       | 19  |

| 6 Peripherals                     | 20  |

| 6.1 Pin Mux                       | 20  |

| 6.2 DMA                           | 23  |

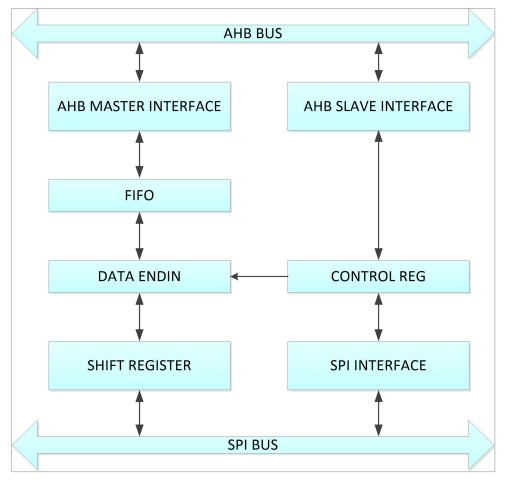

| 6.3 Control SPI Interface         | 42  |

| 6.4 GPIO                          | 55  |

| 6.5 UARTx                         | 65  |

| 6.6 SPIx                          | 102 |

| 6.7 TIMER                         | 121 |

| 6.8 OTP                           | 158 |

| 6.9 GPADC                         | 167 |

| 7 Communication Subsystem         | 169 |

| 7.1 Supported Features            | 169 |

| 7.2 Radio Transceiver             | 169 |

| 7.3 Bluetooth Base band Unit      | 170 |

| 7.4 Performance                   | 170 |

| 8 Package Information             | 173 |

| 9 Ordering Information            | 175 |

| 10 Tape and reel information  | 176 |

|-------------------------------|-----|

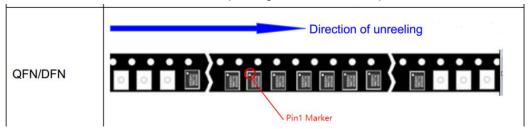

| 10.1 Tape orientation         | 176 |

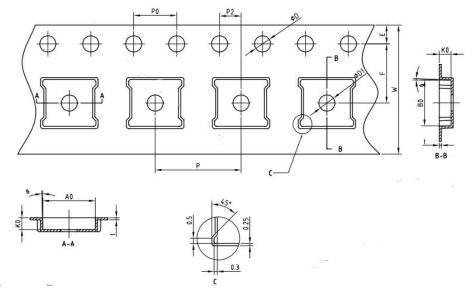

| 10.2 Tape and reel dimensions | 176 |

| 11 Glossary and Abbreviations | 178 |

| 12 Reference Documents        | 179 |

www.onmicro.com.cn 2 / 181

|             | 0, 1, 1                                             |     |

|-------------|-----------------------------------------------------|-----|

| Figure 1.1  | OM6621Dx block diagram                              |     |

| Figure 1.2  | OM6621Dx block diagram                              | 9   |

| Figure 2.1  | OM6621DB chip pin definition                        | 10  |

| Figure 2.2  | OM6621DQ chip pin definition                        | 11  |

| Figure 3.1  | Micro-controller Subsystem                          | 14  |

| Figure 4.1  | Memory Map                                          | 17  |

| Figure 4.2  | APB memory map                                      | 18  |

| Figure 6.1  | Example of DMA Data Transfers                       | 24  |

| Figure 6.2  | Example of Hardware Handshaking                     | 24  |

| Figure 6.3  | Linked List Structure for Chain Transfers           | 25  |

| Figure 6.4  | Data Order at the Destination                       | 26  |

| Figure 6.5  | Data Order at the Destination                       | 27  |

| Figure 6.6  | Data Order at the Destination                       | 27  |

| Figure 6.7  | Specific SPI Device Configuration                   | 44  |

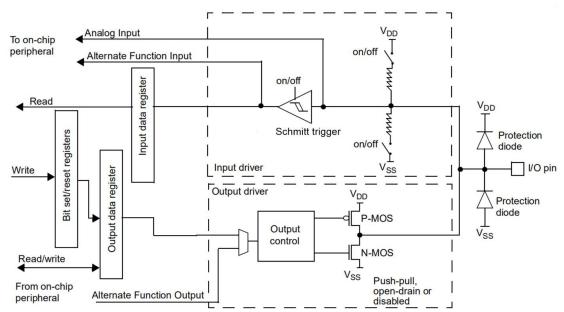

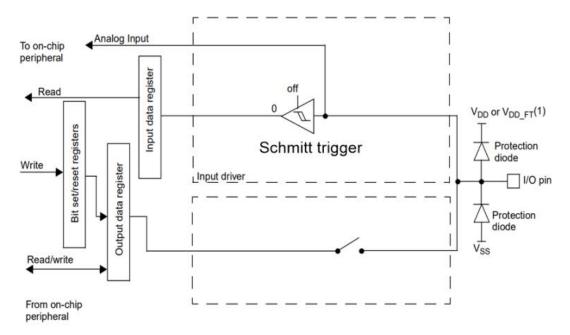

| Figure 6.8  | Basic structure of a standard I/O port bit          | 55  |

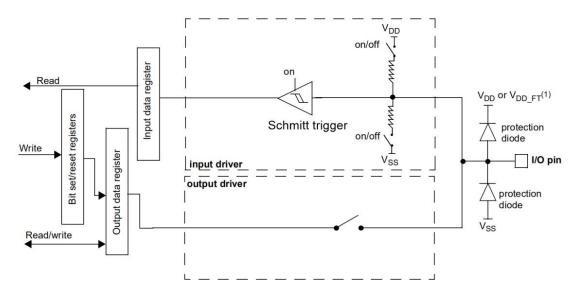

| Figure 6.9  | Input floating/pull up/pull down configurations     | 57  |

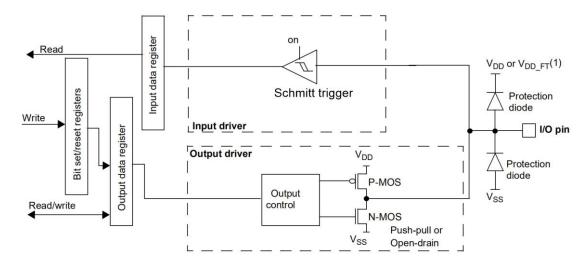

| Figure 6.10 | Output configuration                                | 58  |

| Figure 6.11 | High impedance-analog configuration                 | 58  |

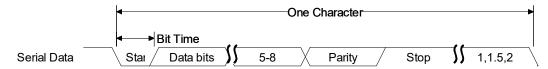

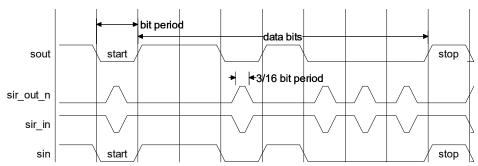

| Figure 6.12 | Serial Data Format                                  | 67  |

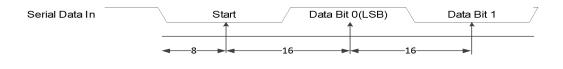

| Figure 6.13 | Receiver Serial Data Sample Points                  | 67  |

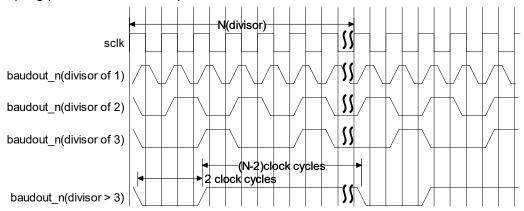

| Figure 6.14 | Baud Clock Reference Timing Diagram                 | 68  |

| Figure 6.15 | IrDA SIR Data Format                                | 68  |

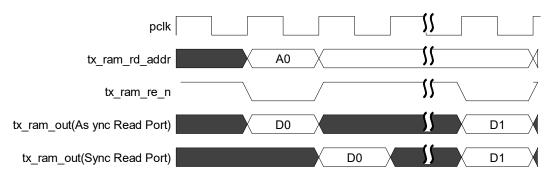

| Figure 6.16 | Timing for RAM Reads                                | 70  |

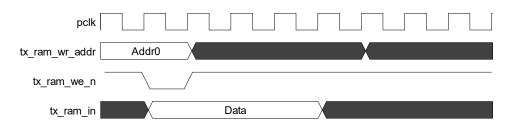

| Figure 6.17 | Timing for RAM Writes                               | 70  |

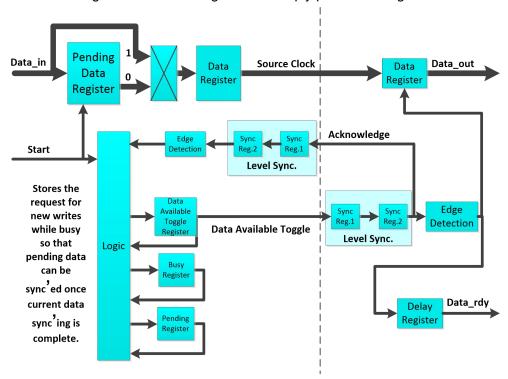

| Figure 6.18 | RTL Diagram of Data Synchronization Module          | 71  |

| Figure 6.19 | Timing Diagram for Data Synchronization Module      | 72  |

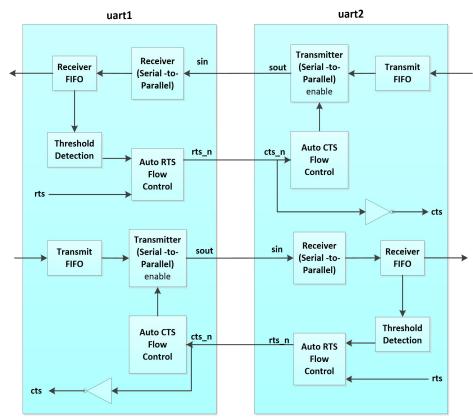

| Figure 6.20 | Auto Flow Control Block Diagram                     | 73  |

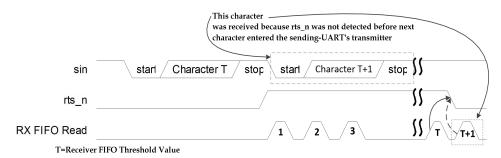

| Figure 6.21 | Auto RTS Timing                                     | 74  |

| Figure 6.22 | Auto CTS Timing                                     | 75  |

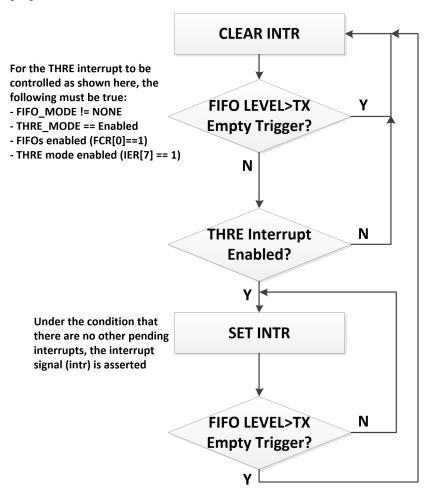

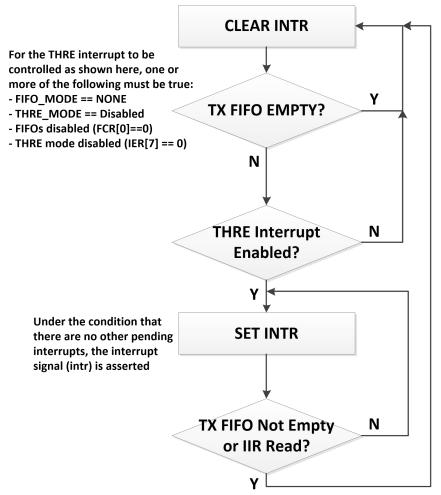

| Figure 6.23 | Flowchart of Interrupt Generation                   | 76  |

| Figure 6.24 | Flowchart of Interrupt generation                   | 77  |

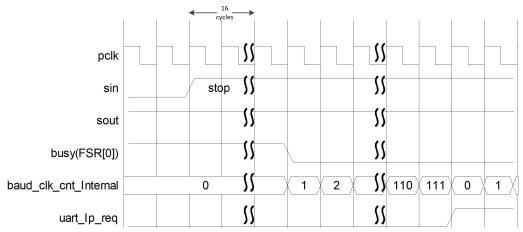

| Figure 6.25 | Clock Gate Enable Timing                            | 78  |

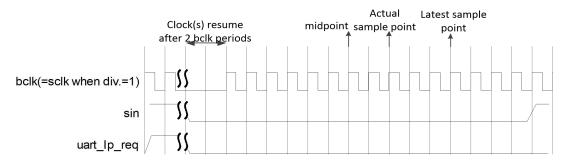

| Figure 6.26 | Resuming Clock(s) After Low Power Mode Timing       | 79  |

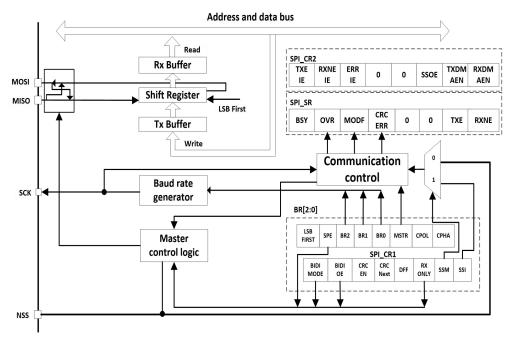

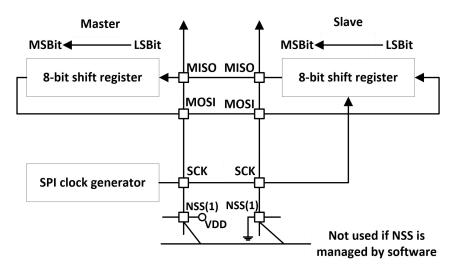

| Figure 6.27 | SPI block diagram                                   | 103 |

| Figure 6.28 | Single master/ single slave application             | 104 |

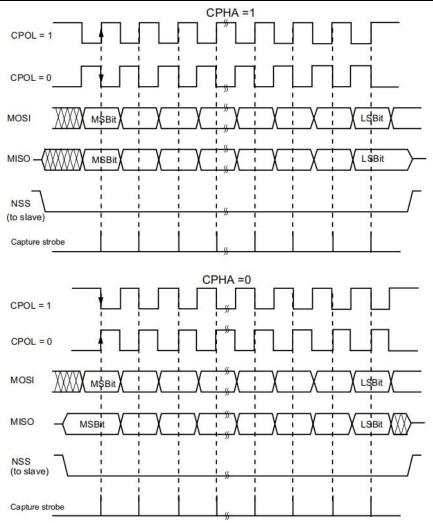

| Figure 6.29 | Data clock timing diagram                           | 106 |

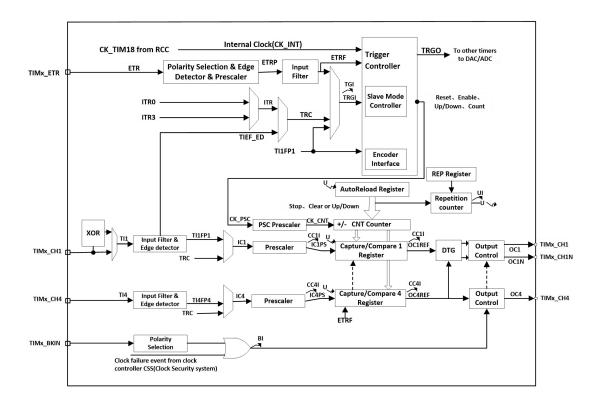

| Figure 6.30 | General timer block                                 | 122 |

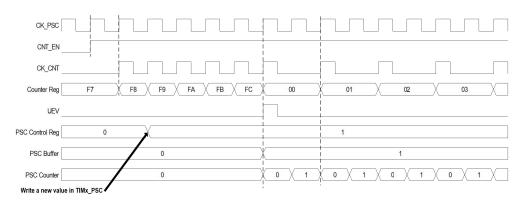

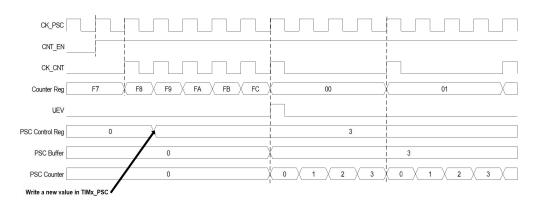

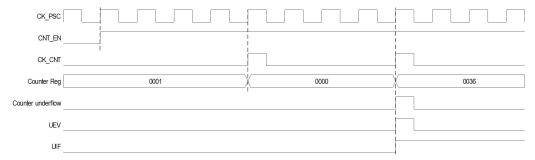

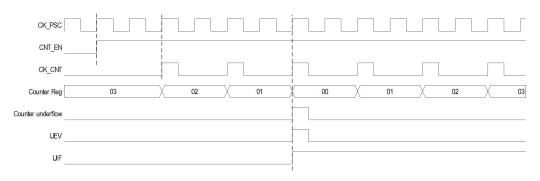

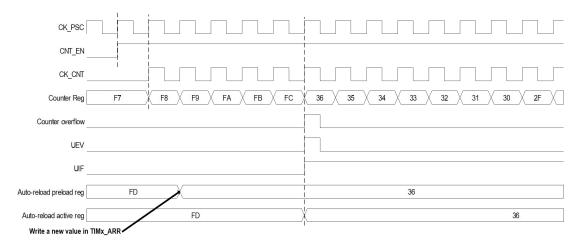

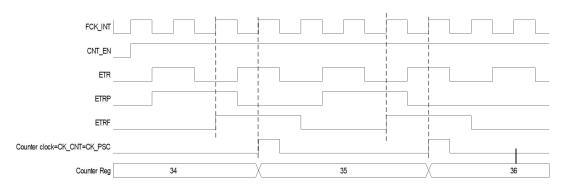

| Figure 6.31 | Counter timing diagram                              | 124 |

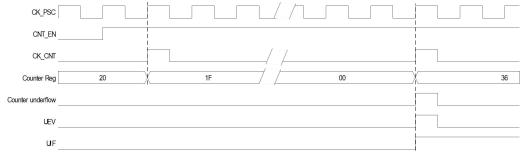

| Figure 6.32 | Counter timing diagram                              | 124 |

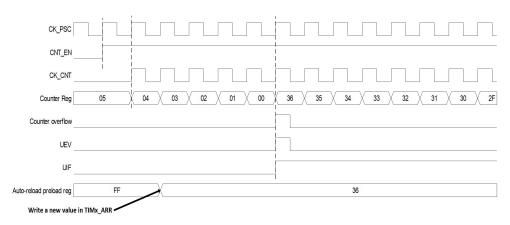

| Figure 6.33 | Counter timing diagram                              | 125 |

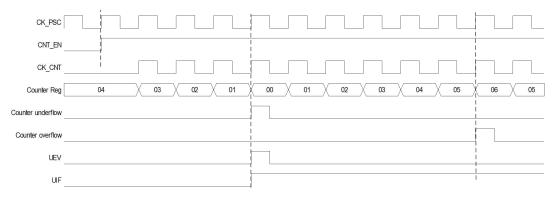

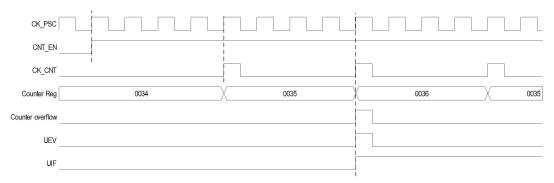

| Figure 6.34 | Counter timing diagram, internal clock divided by 1 | 126 |

| Figure 6.35 | Counter timing diagram, internal clock divided by 2 | 126 |

| Figure 6.36 | Counter timing diagram, internal clock divided by 4 |     |

| Figure 6.37 | Counter timing diagram, internal clock divided by N | 126 |

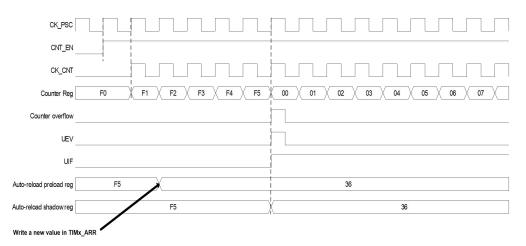

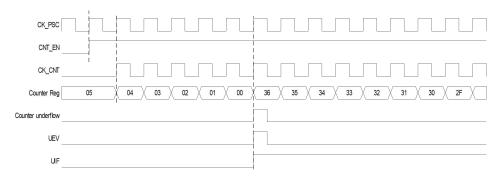

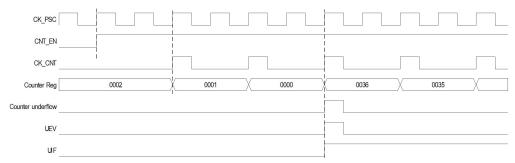

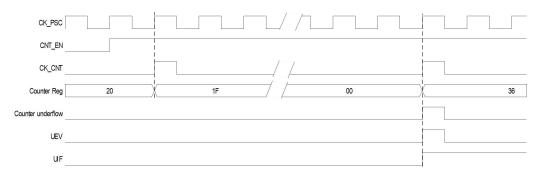

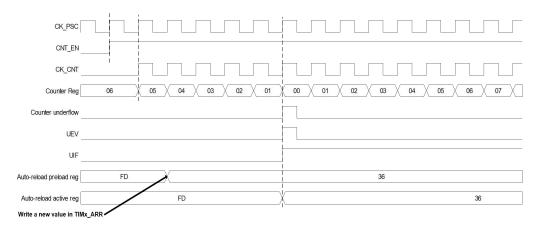

| Figure 6.38 | Counter timing diagram,                                        | 127 |

|-------------|----------------------------------------------------------------|-----|

| Figure 6.39 | Counter timing diagram,                                        | 128 |

| Figure 6.40 | Counter sequence diagram,                                      | 128 |

| Figure 6.41 | Counter timing diagram,                                        | 128 |

| Figure 6.42 | Counter timing diagram, internal clock divided by N            | 129 |

| Figure 6.43 | Counter timing diagram,                                        | 129 |

| Figure 6.44 | Counter timing diagram,                                        | 129 |

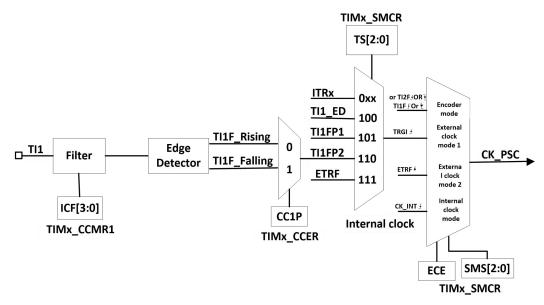

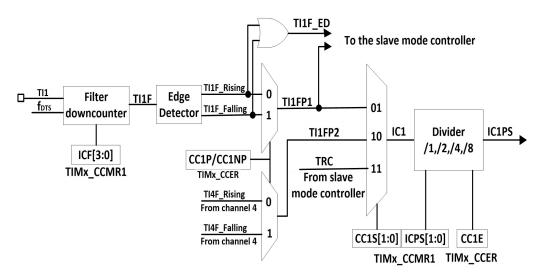

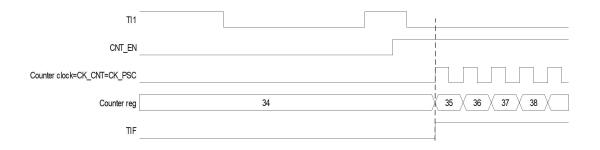

| Figure 6.45 | TI1 external clock connection example                          | 131 |

| Figure 6.46 | Control circuit in external clock mode 1                       | 131 |

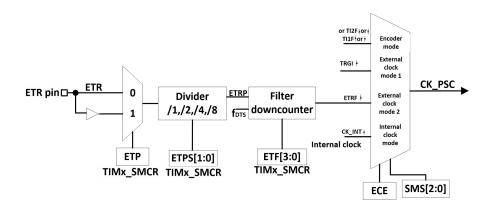

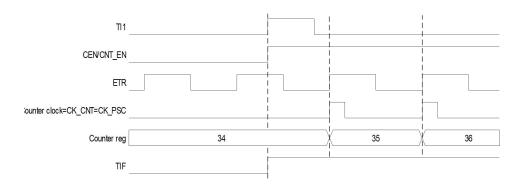

| Figure 6.47 | External trigger input block                                   | 132 |

| Figure 6.48 | Control circuit in external clock mode 2                       | 132 |

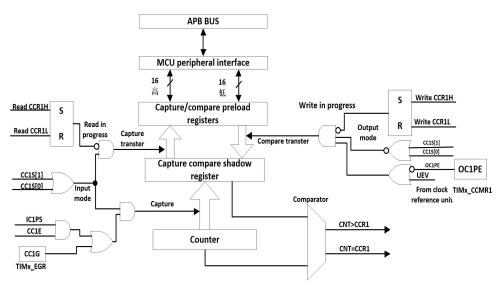

| Figure 6.49 | Capture/compare channel                                        | 133 |

| Figure 6.50 | Main circuit of capture/compare channel 1                      | 133 |

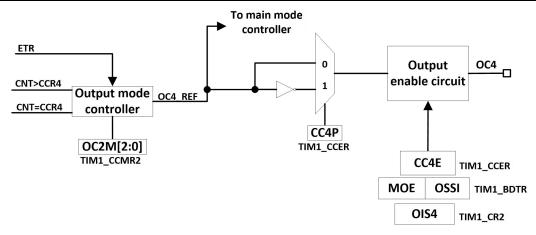

| Figure 6.51 | Capture/compare the output portion of the channel (channel 4)  | 134 |

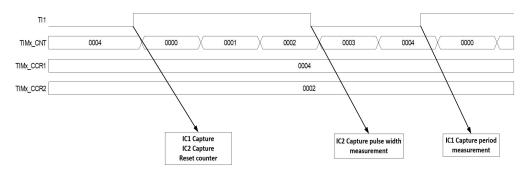

| Figure 6.52 | PWM Input Mode Timing                                          | 136 |

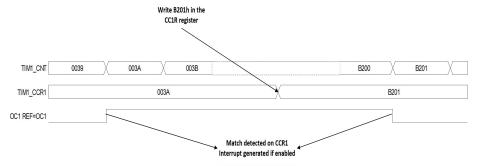

| Figure 6.53 | Output compare mode, toggle on OC1                             | 137 |

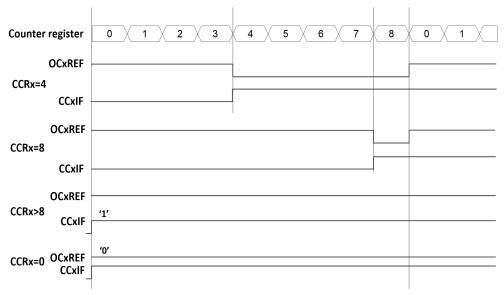

| Figure 6.54 | Edge-aligned PWM waveforms (ARR=8)                             | 138 |

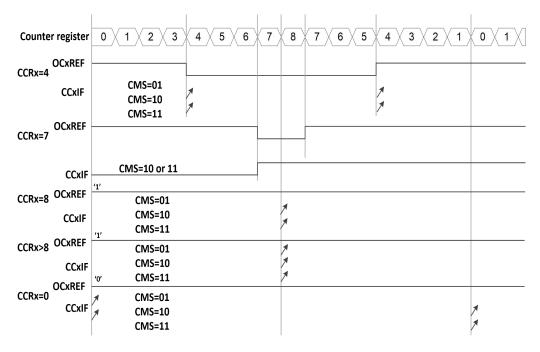

| Figure 6.55 | Center-aligned PWM waveforms (ARR=8)                           | 139 |

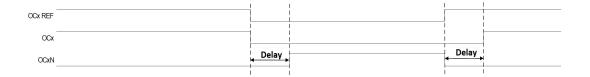

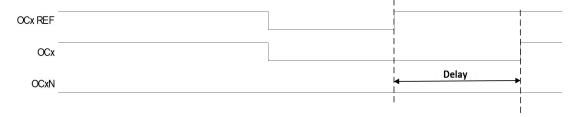

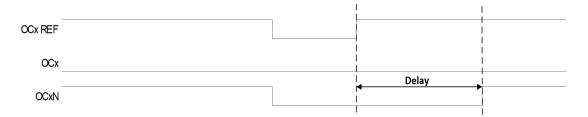

| Figure 6.56 | Complementary output with dead-time insertion                  | 140 |

| Figure 6.57 | Dead-time waveforms with delay greater than the negative pulse | 140 |

| Figure 6.58 | Dead-time waveforms with delay greater than the positive pulse | 141 |

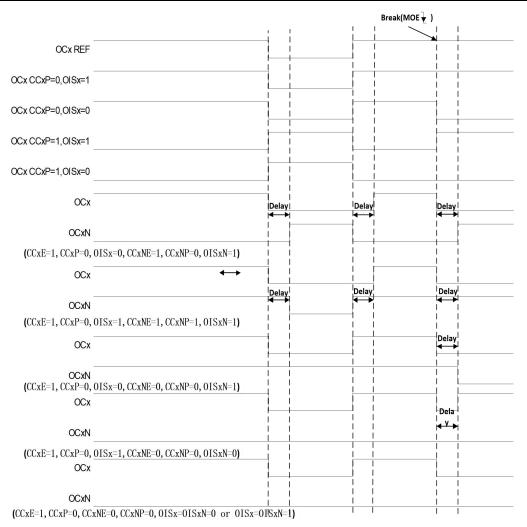

| Figure 6.59 | Output behavior in response to a break                         | 143 |

| Figure 6.60 | Clearing TIMx OCxREF                                           | 144 |

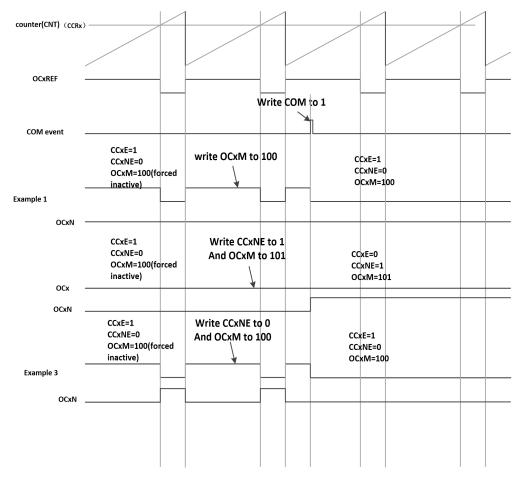

| Figure 6.61 | step generation, COM example (OSSR=1)                          | 145 |

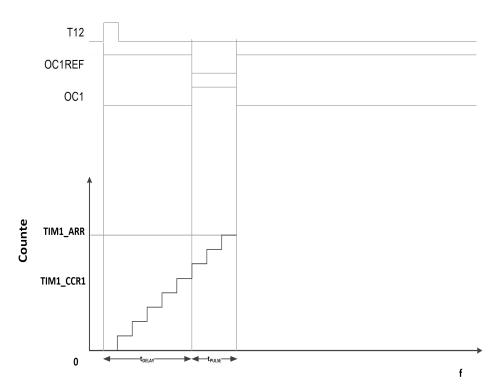

| Figure 6.62 | Example of one pulse mode                                      | 146 |

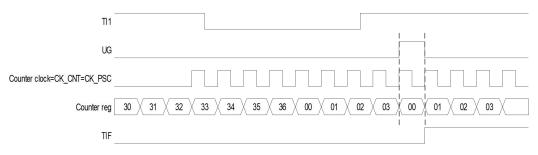

| Figure 6.63 | Control circuit in reset mode                                  | 148 |

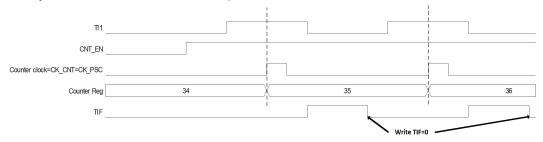

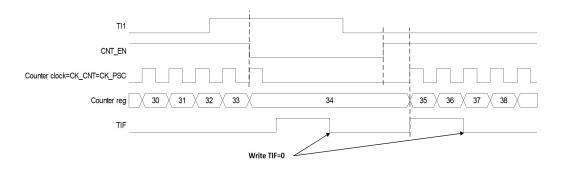

| Figure 6.64 | Control circuit in gated mode                                  | 149 |

| Figure 6.65 | Control circuit in trigger mode                                | 149 |

| Figure 6.66 | Control circuit in external clock mode2 + trigger mode         | 150 |

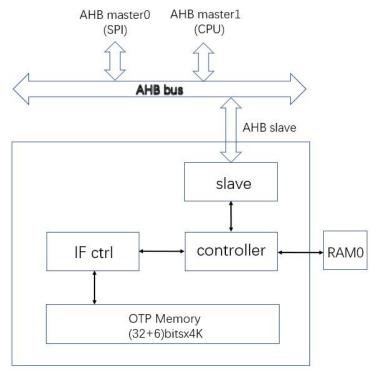

| Figure 6.67 | OTP controller block diagram                                   | 159 |

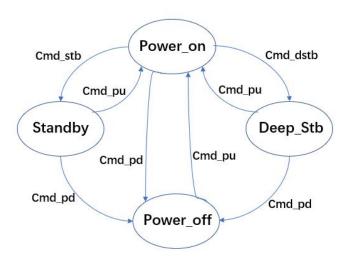

| Figure 6.68 | OTP mem state transfer block                                   | 161 |

| Figure 7.1  | OM6621Dx BT Base band                                          | 170 |

| Figure 8.1  | OM6621DB QFN20 package                                         | 173 |

| Figure 8.2  | OM6621DQ QFN32 package                                         | 174 |

| Figure 10.1 | OM6621DQ Tape Orientation                                      | 176 |

| Figure 10.2 | OM6621DO Tane and Reel Dimensions                              | 176 |

www.onmicro.com.cn 4 / 181

| Table 2.1  | OM6621DB and OM6621DQ pin definition                      | 13  |

|------------|-----------------------------------------------------------|-----|

| Table 3.1  | The MCU interrupt vector                                  | 15  |

| Table 3.2  | OM6621Dx absolute maximum ratings                         | 15  |

| Table 3.3  | OM6621Dx recommend operating conditions                   | 16  |

| Table 3.4  | ESD Characteristic                                        | 16  |

| Table 3.5  | Module Address Mapping                                    | 16  |

| Table 5.1  | Digital Core LDO Specifications                           | 19  |

| Table 5.2  | POR/BOD specifications                                    | 19  |

| Table 6.1  | Peripheral pinmux                                         | 21  |

| Table 6.2  | Format of Linked List Descriptor                          | 25  |

| Table 6.3  | Detection of SCLK values for narrow pulses is not allowed | 69  |

| Table 6.4  | OTP read timing set                                       | 166 |

| Table 6.5  | OTP read speed                                            | 167 |

| Table 7.1  | OM6621Dx BLE Receiver architecture                        | 171 |

| Table 7.2  | OM6621Dx BLE Transceiver architecture                     | 172 |

| Table 8.1  | OM6621DB QFN20 package                                    | 174 |

| Table 8.2  | OM6621DQ QFN32 package                                    | 174 |

| Table 9.1  | OM6621DB and OM6621DQ ordering information                | 175 |

| Table 10.1 | OM6621DQ Common Size                                      | 177 |

| Table 10.2 | OM6621DQ Bag Size                                         | 177 |

| Table 11.1 | Glossary and Abbreviations                                | 178 |

| Table 12.1 | Reference Documents                                       | 179 |

# **Version History**

| Version | Revision                             | Date       | Author | Reviewer |

|---------|--------------------------------------|------------|--------|----------|

| V1.0    | Initial version                      | 2021/05/09 | ZJ     |          |

| V1.1    | Update timer and sflash descriptions | 2021/06/08 | ZJ     |          |

| V1.2    | Update QFN20 information             | 2021/06/29 | ZJ     |          |

| V1.3    | Update Figure3.1 and Figure 6.32     | 2021/08/04 | ZJ     |          |

www.onmicro.com.cn 6 / 181

#### 1 OM6621Dx Overview

## 1.1 Description

The OM6621Dx is a power-optimized true system-on-chip (SOC) solution for both Bluetooth low energy and proprietary 2.4-GHz applications. It integrates a high performance and low power RF transceiver with Bluetooth base band and rich peripheral IO extension.OM6621Dx also integrates a power management to provide high-efficient power management. It targets 2.4-GHz Bluetooth low energy systems, proprietary 2.4-GHz systems, Human-Interface Devices (keyboard, mouse, and remote control), sports and leisure equipment, mobile phone accessories and consumer electronics. OM6621Dx on-chip Bluetooth system compliant with version 5.0.

The chip integrates up to 64MHz high-performance MCU, DMA, GPIO, SPI, UART, TIMER, watch dog, supports 32MHz external crystal, integrates multi-purpose 10bit ADC.

The OM6621Dx integrates on chip 24KB ROM, 24K SRAM, 16K OTP and supports user defined IDE system on chip SFLASH MCU development and JTAG software upgrade.

#### 1.2 Features

- · RF transceiver

- -95dBm at 1Mbps sensitivity Bluetooth® low energy

- TX Power -20 to +10dBm

- 14.1mA peak RX, 12.8mA peak TX (0dBm)

- CPU

- ARM® Cortex™-M4, max 64MHz

- Serial Wire Debug (SWD)

- Memory

- 16KB OTP

- 24KB SRAM

- 24KB ROM

- Serial Flash

- QFN20:2Mb

- QFN32:4Mb

- Icache RAM 2KB

- Clocks

- 32MHz crystal, 32MHz RC, 32.768KHz RC

- Link Controller

- BT 5.0 LE PHY, link controller

- Proprietary 2.4-GHz link controller

- Power Management

www.onmicro.com.cn 7 / 181

- Deep sleep power 2.5uA

- Supply voltage range 1.8V~3.6V

- Integrated Charger(100mA/200mA)

- Software

- compliant with BLE version 5.0

- Supports mesh network

- Network processor interface for applications running on an external micro controller

- · Sample applications and profiles

- Supports 6LowPAN

- Supports OTA

- SWD interface

- Peripherals

- DMA x 4

- UART x 1

- Flexible general-purpose I/O GPIO 19GPIO(max)

- SPI master or slave interface x 1

- PWM x 6

- Watchdog to prevent system dead lock

- 32bit timer x 3

- single-end 10bits GPADC x 4

- AES HE encryption

- Package

- OM6621DB: 20-pin 3x3mm QFN20

- OM6621DQ: 32-pin 4x4mm QFN32

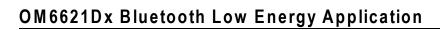

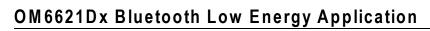

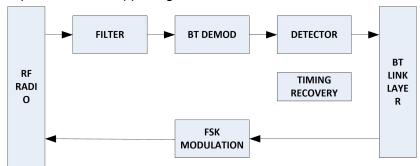

## 1.3 System Function Block Diagram

OM6621Dx is a low power Bluetooth wireless transceiver chip. The chip integrates Bluetooth base band, PHY and proprietary 2.4GHz protocol. The MCU accesses system hardware resource by AHB bus, ROM, RAM, DMA, SFLASH, GPIO exchange data through AHB bus, and all other peripheral is accessed through AHB to APB Bridge and APB bus.

www.onmicro.com.cn 8 / 181

Figure 1.1 OM 6621Dx block diagram

## 1.4 Applications

The OM6621Dx integrated circuit has a fully integrated radio transceiver and base band processor for Bluetooth® Smart. It can be used as an application processor as well as a data pump in fully hosted systems.

Figure 1.2 OM6621Dx block diagram

www.onmicro.com.cn 9 / 181

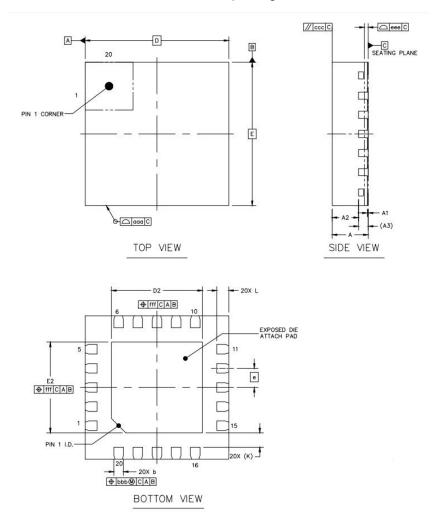

## 2 Pinout

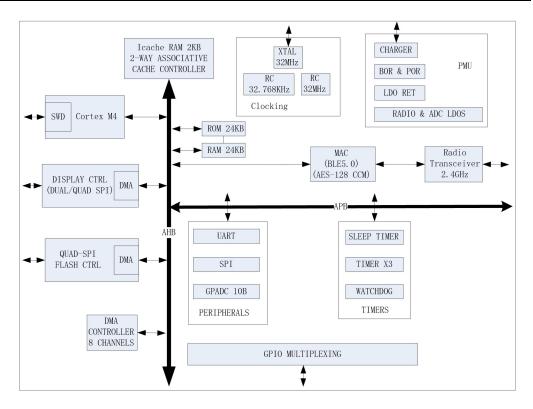

## 2.1 QFN20

The OM6621DB is in the 3mmx3mm QFN20 package. The chip pin definition is as below:

Figure 2.1 OM6621DB chip pin definition

www.onmicro.com.cn 10 / 181

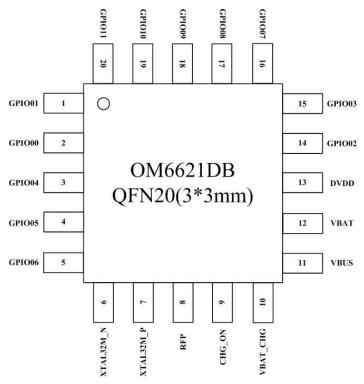

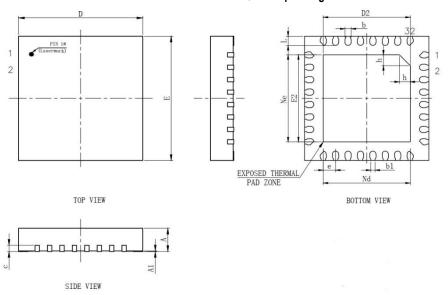

## 2.2 QFN32

The OM6621DQ is in the 4mmx4mm QFN32 package. The chip pin definition is as below:

Figure 2.2 OM6621DQ chip pin definition

www.onmicro.com.cn 11 / 181

# 2.3 Pin Description

| Name                | OM6621DB | OM6621DQ | Туре               | Description               | Note   |

|---------------------|----------|----------|--------------------|---------------------------|--------|

| RESETB              | -        | 1        | Digital            | Reset signal              |        |

| VTAL 22M N          | 6        | 2        | 32M cr             | 32M crystal               |        |

| XTAL32M_N           | 0        | 2        | Analog             | oscillator P input        |        |

| XTAL32M P           | 7        | 3        | Analog             | 32M crystal               |        |

| X I A L S Z I W _ I | ,        | J        | Analog             | oscillator N input        |        |

| NC                  | -        | 4        |                    |                           |        |

| RFP                 | 8        | 5        | RF                 | RF input/output           |        |

| CHG_DIO             | -        | 6        | Analog             | Power supply from charger |        |

| CHG_ON              | 9        | 7        | Analog             | Charge indicator          |        |

| VBAT_CHG            | 10       | 8        | Power              | Battery charge pad        |        |

| VBUS                | 11       | 9        | Power              | Charger power             |        |

| VBAT                | 12       | 10       | Power              | Power supply              |        |

| VBAT                | 12       | 10       | Fower              | 1.8V~3.6V                 |        |

| DVSS                | -        | 11       | Power              | Digital ground            |        |

| DVDD                | 13       | 12       | Power              | Digital Circuit Power     |        |

| GPIO02              | 14       | 13       | Digital/           | Digital                   | Note 1 |

| 01 1002             | 17       | 10       | Analog             | GPIO/GP-ADC input         |        |

| GPIO03              | 15       | 14       | Digital/           | Digital                   | Note 1 |

| 0.1000              |          |          | Analog             | GPIO/GP-ADC input         | 110101 |

| GPIO07              | 16       | 15       | Digital/           | Digital                   | Note 1 |

|                     |          |          | Analog             | GPIO/GP-ADC input         |        |

| GPIO08              | 17       | 16       | Digital/           | Digital                   | Note 1 |

|                     |          |          | Analog             | GPIO/GP-ADC input         |        |

| GPIO09              | 18       | 17       | Digital/           | Digital GPIO              | Note 1 |

|                     |          |          | Analog             |                           |        |

| GPIO10              | 19       | 18       | Digital/<br>Analog | Digital GPIO              | Note 1 |

|                     |          |          | Digital/           |                           |        |

| GPIO11              | 20       | 19       | Analog             | Digital GPIO              | Note 1 |

|                     |          |          | Digital/           |                           |        |

| GPIO12              | -        | 20       | Analog             | Digital GPIO              | Note 1 |

|                     |          |          | Digital/           |                           |        |

| GPIO13              | -        | 21       | Analog             | Digital GPIO              | Note 1 |

| 021011              |          | 22       | Digital/           | D: :: 1 05:0              | NI 4   |

| GPIO14              | -        | 22       | Analog             | Digital GPIO              | Note 1 |

| CDIO45              |          | - 00     | Digital/           | Digital CDIO              | Note 4 |

| GPIO15              | -        |          | Analog             | Digital GPIO              | Note 1 |

www.onmicro.com.cn 12 / 181

| OWOUZIDX | Diuetootii | LOW LITERS | y Appii            | Cation 昂弱     | <b>計</b> 微 |  |  |

|----------|------------|------------|--------------------|---------------|------------|--|--|

| GPIO16   | -          | 24         | Digital/<br>Analog | Digital GPIO  | Note 1     |  |  |

| GPIO17   | -          | 25         | Digital/           | Digital GPIO  | Note 1     |  |  |

| GPIO00   | 2          | 26         | Analog<br>Digital/ | Digital GPIO  | Note 1     |  |  |

| GI 1000  |            | 20         | Analog             | Digital GI 10 | Note 1     |  |  |

| GPIO01   | 1          | 27         | Digital/           | Digital GPIO  | Note 1     |  |  |

|          |            |            | Analog             |               |            |  |  |

| GPIO18   | -          | 28         | Digital/<br>Analog | Digital GPIO  | Note 1     |  |  |

| NC       | -          | 29         |                    |               |            |  |  |

| GPIO04   | 3          | 30         | Digital/<br>Analog | Digital GPIO  | Note 1     |  |  |

| GPIO05   | 4          | 31         | Digital/           | Digital GPIO  | Note 1     |  |  |

|          |            |            |                    |               | Analog     |  |  |

| GPIO06   | 5          | 32         | Digital/           | Digital GPIO  | Note 1     |  |  |

|          |            |            | Analog             |               |            |  |  |

Note 1: All digital peripheral pins can be programmed to any GPIO

Table 2.1 OM6621DB and OM6621DQ pin definition

www.onmicro.com.cn 13 / 181

### 3 MCU Subsystem

OM6621Dx has an MCU subsystem that contains an ARM Cortex-M4 processor, its corresponding buses and peripherals, including all the multiplexing options for the GPIOs, as illustrated in the following figure.

The processor has a 32-bit instruction set with Thumb-2 mode support to use a hybrid of 16-bit and 32-bit instructions to maximize the code performance and density.

MCU memories have a special retention voltage and its control to have the memories in different modes according to the application usage:

- OFF

- ON

- Retention

The following are the supported options for the Cortex-M4:

- NVIC with 52 vectors

- System Tick Timer (SysTick)

- Flash Patch and Breakpoint Unit (FPB)

Figure 3.1 Micro-controller Subsystem

## 3.1 MCU Debug

Serial Wire Debug (SWD) is used for debug.

## 3.2 Interrupts Vector

The following table shows the MCU interrupt vector table for OM6621Dx.

www.onmicro.com.cn 14 / 181

**Num** 0

14

23

24

26

27

31

28-30

15-22

| 5621DX Bluetooth Low Energy Application |                    |     |                 |  |  |

|-----------------------------------------|--------------------|-----|-----------------|--|--|

| ber                                     | Interrupt name     | bit | note            |  |  |

|                                         | BT BB combo        | 1   |                 |  |  |

|                                         | ceva_native_int    | 1   | ceva sleep wake |  |  |

|                                         | DMA combo          | 1   |                 |  |  |

|                                         | GPIO combo         | 1   |                 |  |  |

|                                         | Timer combo        | 1   |                 |  |  |

|                                         | 6200_rf_irq        | 1   |                 |  |  |

|                                         | 6200_rf_spi_irq    | 1   |                 |  |  |

|                                         | PMU_timer          | 1   |                 |  |  |

|                                         | Lcd_spi_int        | 1   |                 |  |  |

|                                         | UART1 combo        | 1   |                 |  |  |

|                                         | otp_int            | 1   |                 |  |  |

| ·                                       | pin_wakeup_int     | 1   |                 |  |  |

| ·                                       | ADC                | 1   |                 |  |  |

| ·                                       | SPI master 0 combo | 1   |                 |  |  |

soft interrupt vtrack interruption

GPIO0 COMBO

**Timers**

indicates AFC need to be redone

Charging and plug interruption

32M crystal oscillator can give digital flag

**OnMicro**

Table 3.1 The MCU interrupt vector

1

1

1

1

1

3

1

## 3.3 Electrical Specifications

charger\_int

SFLASH int

soft\_int

**GPIO**

cc\_intr

Timer

vtrack\_int

cry32m\_dig\_ready

## 3.3.1 Absolute Maximum Ratings

| Parameter                    | Minimum | Maximum | Units |

|------------------------------|---------|---------|-------|

| Supply voltage(VBAT)         | -0.3    | 3.9     | V     |

| Charger voltage(VBUS)        | -0.3    | 6.0     | V     |

| Maximum Junction Temperature | -40     | 125     | °C    |

| Storage Temperature          | -40     | 125     | °C    |

Table 3.2 OM6621Dx absolute maximum ratings

www.onmicro.com.cn 15 / 181

## 3.3.2 Recommend Operating Conditions

| Rating                      | Min     | Тур     | Max     | Unit |

|-----------------------------|---------|---------|---------|------|

| Operation Temperature       | -40     | 1       | 85      | ပ္   |

| Digital Core supply voltage | 0.9     | 1.0     | 1.2     | ٧    |

| RF supply voltage           | 1.1     | 1.25    | 1.4     | V    |

| I/O voltage (Vsupply>3.3)   | 3.1     | 3.3     | 3.5     | ٧    |

| I/O voltage (Vsupply<3.3)   | Vsupply | Vsupply | Vsupply | ٧    |

| Supply voltage(VBAT)        | 1.8     | 3.3     | 3.6     | ٧    |

| Charger voltage(VBUS)       | 4.5     | 5.0     | 5.5     | V    |

Table 3.3 OM6621Dx recommend operating conditions

## 3.3.3 ESD Characteristic

| Parameter | Condition              | Minimum | Typical | Maximum |

|-----------|------------------------|---------|---------|---------|

| HBM       | Test method:           | -       | ±4000 V | ±8000 V |

|           | ESDA/JEDEC JS-001-2017 |         |         |         |

| MM        | All pins, test method: | -       | -       | ±200 V  |

|           | JESD22 -A115C          |         |         |         |

| CDM       | All pins, test method: | -       | -       | ±1000 V |

|           | ESDA/JEDEC JS-002-2018 |         |         |         |

Table 3.4 ESD Characteristic

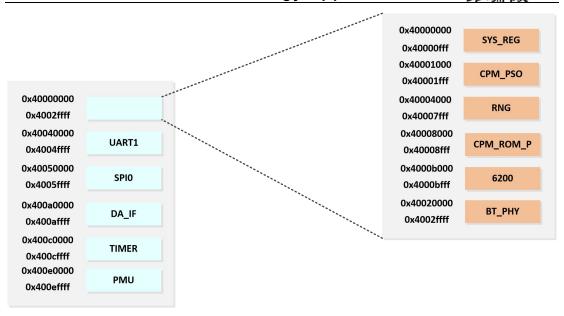

## 3.4 Module Address Mapping

| Base Address | Module    |  |  |

|--------------|-----------|--|--|

| 0x4000000    | SYS_REG   |  |  |

| 0x40001000   | CPM_PSO   |  |  |

| 0x40004000   | RNG       |  |  |

| 0x40008000   | CPM_ROM_P |  |  |

| 0x4000B000   | 6200      |  |  |

| 0x40020000   | BT_PHY    |  |  |

| 0x40040000   | UART1     |  |  |

| 0x40050000   | SPI0      |  |  |

| 0x400A0000   | DA_IF     |  |  |

| 0x400C0000   | TIMER     |  |  |

| 0x400E0000   | PMU       |  |  |

Table 3.5 Module Address Mapping

www.onmicro.com.cn 16 / 181

### 4 Memory

## 4.1 Memory Introduction

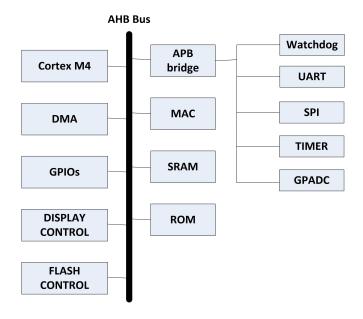

OM6621Dx SOC memory includes ROM, SRAM and stacked flash for code and data storage. The CPU and peripheral devices can access the memory. The CPU can access the peripherals as well. The address mapping of the memories and devices are explained in the following sections.

## 4.2 Memory Map

Figure 4.1 Memory Map

## 4.3 APB Address Space

The following figure shows the details of Advanced Peripheral Bus (APB) portion of the memory map.

www.onmicro.com.cn 17 / 181

Figure 4.2 APB memory map

www.onmicro.com.cn 18 / 181

#### 5 PMU

### 5.1 Power Management

There are three different power modes in the OM6621Dx:

- Active Mode: System is active and operates at full speed.

- Sleep Mode: No power gating has been programmed; the CPU is idle, waiting for an interrupt.32M crystal is on, 32K RC is on. Peripherals is depending on the programmed enabled value.

- Extended Sleep Mode: All power domains are off except for the always on power domain, the programmed Bluetooth timer module, 32M crystal is off, 32K RC is on. The data retention SRAM retains its data and other SRAM is power off. It is wake by timer or GPIOs.

## 5.2 Digital LDO

Digital LDO regulates the DC-DC converter to supply power to all the Digital Logic and Memory blocks.

| Parameter         | Symbol | Min | Тур | Max | Unit | Comment |

|-------------------|--------|-----|-----|-----|------|---------|

| Input Voltage     |        |     | 3.3 |     | V    |         |

| Output Voltage    |        |     | 1.0 |     | V    |         |

| External Load Cap |        |     | 1.0 |     | μF   |         |

Table 5.1 Digital Core LDO Specifications

#### 5.3 POR/BOD

Power-on Reset (POR) circuit holds the system at reset while the supply reaches the required voltage level. Brown-out detector (BOD) circuit puts the system into reset state when the supply falls below the Brown-out Threshold.

| Parameter           | Symbol | Min | Тур | Max | Unit | Comment |

|---------------------|--------|-----|-----|-----|------|---------|

| Brown Out Threshold |        |     | 1.4 |     | V    |         |

Table 5.2 POR/BOD specifications

www.onmicro.com.cn 19 / 181

## 6 Peripherals

### 6.1 Pin Mux

#### 6.1.1 Introduction

OM6621Dx has a configurable pin multiplexing module (Pin MUX) which can bring different peripherals on different GPIOs.

#### 6.1.2 Main Features

pinmux has the following features:

- There are 41 mux choices for the Peripheral pinmux.

- Peripheral pinmux can be config by REG\_GPIOX\_MUX.

### 6.1.3 Function Description

The pin multiplexing choices for all pads are shown in the following table.

There are more mux choices for the Pin Mux. When you pick a mux choice for an interface, make sure that all signal of the interface should be configured to the picked mux choice. The following pin mux tables set the signals of an interface.

| NAME                      | NUMBER |

|---------------------------|--------|

| PINMUX_JTAG_MODE_CFG      | 0      |

| PINMUX_DBG_MODE_CFG       | 1      |

| PINMUX_SPI0_MST_SDA_I_CFG | 3      |

| PINMUX_SPI0_MST_SDA_O_CFG | 4      |

| PINMUX_SPI0_MST_CSN_CFG   | 5      |

| PINMUX_SPI0_MST_SCK_CFG   | 6      |

| PINMUX_SFLASH_SI_CFG      | 8      |

| PINMUX_SFLASH_SO_CFG      | 9      |

| PINMUX_SFLASH_HD_CFG      | 10     |

| PINMUX_SFLASH_WP_CFG      | 11     |

| PINMUX_SFLASH_CK_CFG      | 12     |

| PINMUX_SFLASH_CSN_CFG     | 13     |

| PINMUX_UART1_SDA_I_CFG    | 15     |

| PINMUX_UART1_SDA_O_CFG    | 16     |

| PINMUX_UART1_CTS_I_N_CFG  | 17     |

| PINMUX_UART1_RTS_O_N_CFG  | 18     |

www.onmicro.com.cn 20 / 181

| OWIGOZIDA DIGEROOTII LOW LITETSY | Application 昂瑞微 |  |  |

|----------------------------------|-----------------|--|--|

| PINMUX_TX_EXT_PD_CFG             | 19              |  |  |

| PINMUX_RX_EXT_PD_CFG             | 20              |  |  |

| PINMUX_GPIO_ADC_CFG              | 26              |  |  |

| PINMUX_GPIO_MODE_CFG             | 28              |  |  |

| PINMUX_SFLASH1_CSN_1_CFG         | 24              |  |  |

| PINMUX_SFLASH1_SI_CFG            | 25              |  |  |

| PINMUX_SFLASH1_SO_CFG            | 28              |  |  |

| PINMUX_SFLASH1_HD_CFG            | 30              |  |  |

| PINMUX_SFLASH1_WP_CFG            | 31              |  |  |

| PINMUX_SFLASH1_CK_CFG            | 32              |  |  |

| PINMUX_SFLASH1_CSN_CFG           | 33              |  |  |

| PINMUX_TIMER0_ETR_CFG            | 34              |  |  |

| PINMUX_TIMER1_ETR_CFG            | 35              |  |  |

| PINMUX_TIMER2_ETR_CFG            | 36              |  |  |

| PINMUX_TIMER0_BKIN_CFG           | 37              |  |  |

| PINMUX_TIMER1_BKIN_CFG           | 38              |  |  |

| PINMUX_TIMER2_BKIN_CFG           | 39              |  |  |

| PINMUX_TIMER0_IO_0_CFG           | 40              |  |  |

| PINMUX_TIMER0_IO_1_CFG           | 41              |  |  |

| PINMUX_TIMER0_TOGGLE_N_0_CFG     | 44              |  |  |

| PINMUX_TIMER1_IO_0_CFG           | 47              |  |  |

| PINMUX_TIMER1_IO_1_CFG           | 48              |  |  |

| PINMUX_TIMER1_TOGGLE_N_0_CFG     | 51              |  |  |

| PINMUX_TIMER2_IO_0_CFG           | 54              |  |  |

| PINMUX_TIMER2_IO_1_CFG           | 55              |  |  |

| PINMUX_TIMER2_TOGGLE_N_0_CFG     | 58              |  |  |

|                                  |                 |  |  |

Table 6.1 Peripheral pinmux

## 6.1.4 Pin MUX Register Map

| Address    | Name           | Description    |

|------------|----------------|----------------|

| 0X40000080 | PIN_MUX_CTRL_1 | Pinmux control |

| 0X40000084 | PIN_MUX_CTRL_2 | Pinmux control |

| 0X40000088 | PIN_MUX_CTRL_3 | Pinmux control |

| 0X4000008C | PIN_MUX_CTRL_4 | Pinmux control |

| 0X40000090 | PIN_MUX_CTRL_5 | Pinmux control |

### PIN\_MUX\_CTRL\_1 address: 0x40000080

| Bit | R/W | Reset | Name | Description |

|-----|-----|-------|------|-------------|

| 31  | N/A | 0x0   | N/A  | reserved    |

www.onmicro.com.cn 21 / 181

| A 04 | • 0        |

|------|------------|

|      | Jicro      |

|      | 11010      |

| 昂到   | <b>治</b> 微 |

|       |    |     | 0,            |                  |  |

|-------|----|-----|---------------|------------------|--|

| 30:24 | RW | 0x0 | gpio3_mux_reg | gpio3 mux config |  |

| 22:16 | RW | 0x0 | gpio2_mux_reg | gpio2 mux config |  |

| 14:8  | RW | 0x0 | gpio1_mux_reg | gpio1 mux config |  |

| 6:0   | RW | 0x0 | gpio0_mux_reg | gpio0 mux config |  |

#### PIN\_MUX\_CTRL\_2 address: 0x40000084

| Bit   | R/W | Reset | Name          | Description      |

|-------|-----|-------|---------------|------------------|

| 31    | N/A | 0x0   | N/A           | reserved         |

| 30:24 | RW  | 0x0   | gpio7_mux_reg | gpio7 mux config |

| 23    | N/A | 0x0   | N/A           | reserved         |

| 22:16 | RW  | 0x0   | gpio6_mux_reg | gpio6 mux config |

| 15    | N/A | 0x0   | N/A           | reserved         |

| 14:8  | RW  | 0x0   | gpio5_mux_reg | gpio5 mux config |

| 7     | N/A | 0x0   | N/A           | reserved         |

| 6:0   | RW  | 0x0   | gpio4_mux_reg | gpio4 mux config |

#### PIN\_MUX\_CTRL\_3 address: 0x40000088

| Bit   | R/W | Reset | Name           | Description       |

|-------|-----|-------|----------------|-------------------|

| 31    | N/A | 0x0   | N/A            | reserved          |

| 30:24 | RW  | 0x0   | gpio11_mux_reg | gpio11 mux config |

| 23    | N/A | 0x0   | N/A            | reserved          |

| 22:16 | RW  | 0x0   | gpio10_mux_reg | gpio10 mux config |

| 15    | N/A | 0x0   | N/A            | reserved          |

| 14:8  | RW  | 0x0   | gpio9_mux_reg  | gpio9 mux config  |

| 7     | N/A | 0x0   | N/A            | reserved          |

| 6:0   | RW  | 0x0   | gpio8_mux_reg  | gpio8 mux config  |

#### PIN MUX CTRL 4 address: 0x4000008C

| Bit   | R/W | Reset | Name           | Description       |

|-------|-----|-------|----------------|-------------------|

| 31    | N/A | 0x0   | N/A            | reserved          |

| 30:24 | RW  | 0x1c  | gpio15_mux_reg | gpio15 mux config |

| 23    | N/A | 0x0   | N/A            | reserved          |

| 22:16 | RW  | 0x0   | gpio14_mux_reg | gpio14 mux config |

| 15    | N/A | 0x0   | N/A            | reserved          |

| 14:8  | RW  | 0x0   | gpio13_mux_reg | gpio13 mux config |

| 7     | N/A | 0x0   | N/A            | reserved          |

| 6:0   | RW  | 0x0   | gpio12_mux_reg | gpio12 mux config |

#### PIN\_MUX\_CTRL\_5 address: 0x40000090

|   | Bit   | R/W | Reset | Name           | Description       |

|---|-------|-----|-------|----------------|-------------------|

|   | 31:23 | N/A | 0x0   | N/A            | reserved          |

| ĺ | 22:16 | RW  | 0x1c  | gpio18_mux_reg | gpio18 mux config |

www.onmicro.com.cn 22 / 181

| <b>^</b> | 0     |

|----------|-------|

|          | Nicro |

|          |       |

| 昂        | 瑞微    |

|      |     |      |                | 5111              |

|------|-----|------|----------------|-------------------|

| 15   | N/A | 0x0  | N/A            | reserved          |

| 14:8 | RW  | 0x1c | gpio17_mux_reg | gpio17 mux config |

| 7    | N/A | 0x0  | N/A            | reserved          |

| 6:0  | RW  | 0x1c | gpio16_mux_reg | gpio16 mux config |

#### 6.2 DMA

#### 6.2.1 Introduction

Onmicro™ DMA is a direct memory access controller which transfers regions of data efficiently on bus.

#### 6.2.2 Main Features

- Compliant with AMBA™ 2 AHB protocol specification.

- Supports up to 8 DMA channels.

- Supports up to 16 request/acknowledge pairs for hardware handshaking.

- Provides the round-robin arbitration with 2 priority levels.

- Supports 8/16/32-bit wide data transfer.

### 6.2.3 Function Description

DMA supports up to 8 DMA channels. Each DMA channel provides a set of registers to describe the intended data transfers. Multiple DMA channels can be enabled concurrently, but the DMA controller services one channel at a time.

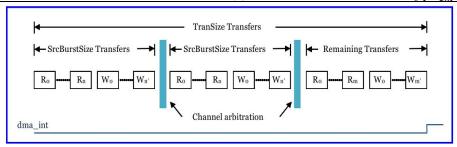

The following figure shows an illustration of data transfer timing for a channel. To prevent channels from being starved, the DMA controller services all ready-channels alternatively, performing at most SrcBurstSize data transfers each time. Consequently, the data transfers of a channel may be split into several chunks when the total transfer size (TranSize) is larger than the source burst size (SrcBurstSize). When the overall data transfers of a channel complete, the DMA controller will update the interrupt status register, IntStatus, and assert the dma\_int interrupt signal if the terminal count interrupt is enabled.

The data transfers of a channel will be stopped when an error occurs. The data transfers of a channel can also be aborted by software. In either case, the DMA controller will disable the channel, and assert dma\_int if the corresponding interrupt is enabled.

www.onmicro.com.cn 23 / 181

Figure 6.1 Example of DMA Data Transfers

#### 6.2.3.1 Channel Arbitration

DMA provides two priority levels for channel arbitration. Every channel is associated with a priority level by the Priority field of the channel control register, ChnCtrl. During the channel arbitration, the DMA controller selects a high priority channel first. A low priority channel is only selected if there is no high priority channel. Channels of the same priority level will be selected by the round-robin scheme.

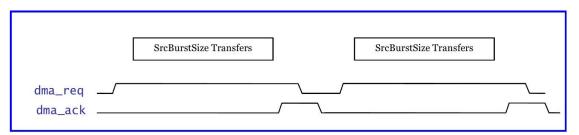

#### 6.2.3.2 Hardware Handshak

DMA provides up to 16 pairs of hardware handshake signals ( dma\_req/dma\_ack ) for data transfers with low-speed devices. The following figure gives an example of hardware handshaking. The device should assert dma\_req only when it prepares enough data to transfer or when it has enough empty space to receive the incoming data. The DMA controller only issues bus requests to read/write the data when it sees the dma\_req asserted, avoiding holding the bus in the wait state indefinitely. The DMA controller asserts dma\_ack when it completes SrcBurstSize data transfers from/to the device. The device should de-assert dma\_req after detecting the assertion of dma\_ack . The DMA controller should de-assert dma\_ack after detecting the de-assertion of dma\_req . If an error is encountered during the data transfers, the DMA controller will disable the channel without asserting dma\_ack. The error handling software should reset both the source and destination of the DMA transfer to deassert dma\_req.

Figure 6.2 Example of Hardware Handshaking

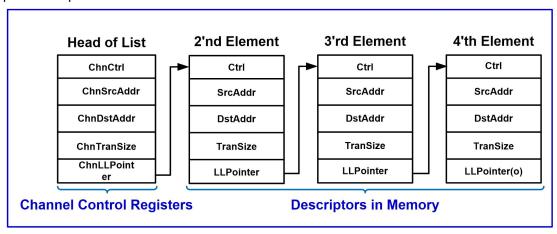

#### 6.2.3.3 Chain Transfer

www.onmicro.com.cn 24 / 181

DMA provides the chain transfer function, with which multiple blocks of data can be transferred consecutively without the intervention of the main processor.

Before a chain transfer is started, a linked list structure must be built to describe the data blocks to move and the associated control setups. The first element of the list (the head of the list) is described by the channel control registers. The rest of elements of the list are specified by the linked list descriptors stored in the memory, where the linked list descriptor holds the control values to load to the channel control registers to continue the data transfer. The following figure shows an example of the linked list structure.

When the channel is enabled, the DMA controller will first transfer data according to the channel control registers. After the data transfer completes, the DMA controller will continue the data transfer by following the ChnLLPointer. The content of the linked list descriptor pointed by ChnLLPointer will be loaded to the channel control registers if ChnLLPointer is not zero. The loaded descriptor becomes the new head of the list and this process repeats until the ChnLLPointer is zero.

Figure 6.3 Linked List Structure for Chain Transfers

When the terminal count interrupt (IntTCMask) of a channel is enabled, the DMA controller will generate an interrupt and disable the channel when the data transfer for the head of the list is done. If the ChnLLPointer is not zero, the channel control registers will be preloaded with the next descriptor before the interrupt is generated. The interrupt handling software could resume the chain transfer by just re-enabling the channel.

The following table shows the format of the linked list descriptor. The bit field definition of each descriptor word is the same as the corresponding channel control register except the channel enable bit, which is reserved in the linked list descriptor.

| Name      | Offset | Description         | Format               |

|-----------|--------|---------------------|----------------------|

| Ctrl      | 0x00   | Channel control     | See DMA Register Map |

| SrcAddr   | 0x04   | Source address      | See DMA Register Map |

| DstAddr   | 0x08   | Destination address | See DMA Register Map |

| TranSize  | 0x0c   | Total transfer size | See DMA Register Map |

| LLPointer | 0x10   | Linked list pointer | See DMA Register Map |

Table 6.2 Format of Linked List Descriptor

#### 6.2.3.4 Data Order

www.onmicro.com.cn 25 / 181

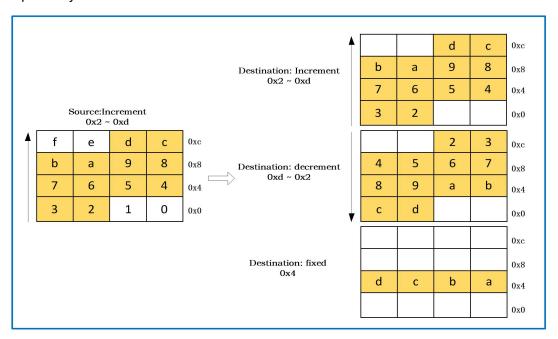

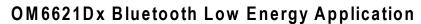

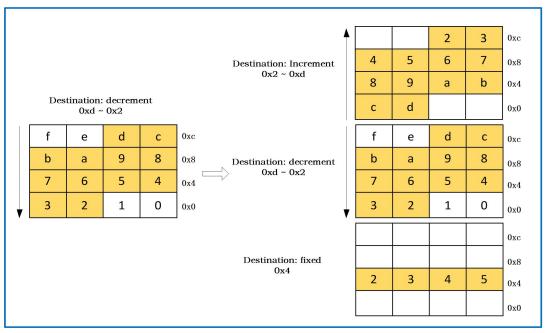

DMA provides three address control modes: increment mode, decrement mode, and fixed mode. At the increment mode, the address is increased after the DMA controller accesses a data of the source/destination. At the decrement mode, the address is decreased after the DMA controller accesses a data of the source/destination. At the fixed mode, the address remains unchanged after the DMA controller accesses a data of the source/destination.

When the address control mode of the source is the same as that of the destination, the DMA controller maintains the same byte order of the data between the source and the destination. When the address control mode of the source is opposite to that of the destination, the data written to the destination will be in the reverse byte order of that read from the source. The data order of the fixed mode is treated the same as that of the increment mode. Figure 6.4, Figure 6.5 and Figure 6.6 illustrate the byte order of the data at the destination when the source address mode is increment, decrement, and fixed respectively.

Figure 6.4 Data Order at the Destination when the Source Address Mode is the Increment Mode

www.onmicro.com.cn 26 / 181

Figure 6.5 Data Order at the Destination when the Source Address Mode is the Decrement Mode

Figure 6.6 Data Order at the Destination when the Source Address Mode is the Fixed Mode

## 6.2.4 DMA Register Map

| offset | Name  | Description              |

|--------|-------|--------------------------|

| 0x00   | IdRev | ID and revision register |

| 0x04   | NA    | Reserved                 |

| 0x08   | NA    | Reserved                 |

www.onmicro.com.cn 27 / 181

| 0x0C        | NA           | Reserved                               |

|-------------|--------------|----------------------------------------|

| 0x10        | DMACfg       | DMAC configuration register            |

| 0x14        | NA           | Reserved                               |

| 0x18        | NA           | Reserved                               |

| 0x1C        | NA           | Reserved                               |

| 0x20        | DMACtrl      | DMAC control register                  |

| 0x24        | NA           | Reserved                               |

| 0x28        | NA           | Reserved                               |

| 0x2C        | NA           | Reserved                               |

| 0x30        | IntStatus    | Interrupt status register              |

| 0x34        | ChEN         | Channel enable register                |

| 0x38        | NA           | Reserved                               |

| 0x3C        | NA           | Reserved                               |

| 0x40        | ChAbort      | Channel abort register                 |

| 0x44+n*0x14 | ChnCtrl      | Channel n control register             |

| 0x48+n*0x14 | ChnSrcAddr   | Channel n source address register      |

| 0x4C+n*0x14 | ChnDstAddr   | Channel n destination address register |

| 0x50+n*0x14 | ChnTranSize  | Channel n transfer size register       |

| 0x54+n*0x14 | ChnLLPointer | Channel n linked list pointer register |

|             |              | · · · · · · · · · · · · · · · · · · ·  |

#### **DMA Register Description**

The following sections describe DMA registers in detail. The abbreviations for the Type column are summarized below:

RO: read only WO: write only

R/W: readable and writable

R/W1C: readable and write 1 to clear ID and Revision Register(offset 0x00)

This register holds the ID number and revision number. The reset values of the two revision fields are revision dependent.

| Bit   | R/W | Reset     | Name     | Description           |

|-------|-----|-----------|----------|-----------------------|

| 31:12 | R   | 0x01021   | ID       | ID number for DMAC    |

| 11:4  | R   | Revision  | RevMajor | Major revision number |

|       |     | dependent |          |                       |

| 3:0   | R   | Revision  | RevMinor | Minor revision number |

|       |     | dependent |          |                       |

#### DMAC Configuration Register(offset 0x10)

| Bit | R/W | Reset         | Name     | Description                        |

|-----|-----|---------------|----------|------------------------------------|

| 31  | R   | Configuration | ChainXfr | Chain transfer                     |

|     |     | dependent     |          | 0=chain transfer is not configured |

|     |     |               |          | 1=chain transfer is configured     |

www.onmicro.com.cn 28 / 181

| 30    | R  | Configuration | RevMajor   | Major revision number                     |

|-------|----|---------------|------------|-------------------------------------------|

|       |    | dependent     |            |                                           |

| 29:15 | NA | Configuration | ReqSync    | DMA request synchronization.              |

|       |    | dependent     |            | The DMA request synchronization should    |

|       |    |               |            | be configured to avoid signal integrity   |

|       |    |               |            | problems when the request signal is not   |

|       |    |               |            | clocked by the system bus clock, which    |

|       |    |               |            | the DMA control logic operates in. If the |

|       |    |               |            | request synchronization is not            |

|       |    |               |            | configured, the request signal is sampled |

|       |    |               |            | directly without synchronization.         |

|       |    |               |            | 0=request synchronization is not          |

|       |    |               |            | configured                                |

|       |    |               |            | 1=request synchronization is configured   |

| 14:10 | R  | Configuration | ReqNum     | Request/acknowledge number                |

|       |    | dependent     |            |                                           |

| 9:4   | R  | Configuration | FIFO Depth | FIFO depth                                |

|       |    | dependent     |            |                                           |

| 3:0   | R  | Configuration | ChannelNu  | Channel number                            |

|       |    | dependent     | m          |                                           |

|       |    |               |            |                                           |

#### DMAC Control Register (offset 0x20)

| Bit  | R/W | Reset | Name     | Description                                                                               |

|------|-----|-------|----------|-------------------------------------------------------------------------------------------|

| 31:1 | NA  | NA    | Reserved | NA                                                                                        |

| 0    | W   | 0x0   | Reset    | Software reset control. Set this bit to 1 to reset the DMA core and disable all channels. |

#### Interrupt Status Register(offset 0x30)

This register contains the terminal count, error, and abort status. The terminal count status of a channel is asserted when the channel encounters the terminal counter event. The error/abort status of a channel is asserted when the channel encounters the error/abort event. There is one bit of status for each channel and the status bit is zero when the corresponding channel is not configured.

| Bit   | R/W   | Reset | Name     | Description                                                                                                                                                                                                    |

|-------|-------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | NA    | NA    | Reserved | NA                                                                                                                                                                                                             |

| 23:16 | R/W₁C | 0x0   | TC       | The terminal count status of DMA channels, one bit per channel. The terminal count status is asserted when a channel transfer finishes without abort or error event.  0=channel N has no terminal count status |

|       |       |       |          | 1=channel N has terminal count status                                                                                                                                                                          |

www.onmicro.com.cn 29 / 181

| 15:8 | R/W₁C | 0x0 | Abort | The abort status of channel, one bit per                                                                                                                                                                                                                                          |

|------|-------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |       |     |       | channel.                                                                                                                                                                                                                                                                          |

|      |       |     |       | The abort status is asserted when a channel                                                                                                                                                                                                                                       |

|      |       |     |       | transfer is aborted.                                                                                                                                                                                                                                                              |

|      |       |     |       | 0=channel N has no abort status                                                                                                                                                                                                                                                   |

|      |       |     |       | 1=channel N has abort status                                                                                                                                                                                                                                                      |

| 7:0  | R/W₁C | 0x0 | Error | The error status, one bit per channel. The error status is asserted when a channel transfer encounters the following error events:  Bus error  Unaligned address  Unaligned transfer width  Reserved configuration  0=channel N has no error status  1=channel N has error status |

#### Channel Enable Register (Offset 0x34)

The register shows the DMA channel enable status. The status fields only exist when the corresponding channels are configured. This register is an alias of the Enable fields of all ChnCtrl registers.

| Bit | R/W | Reset | Name | Description                                        |

|-----|-----|-------|------|----------------------------------------------------|

| N:0 | R   | 0x0   | ChEN | Alias of the Enable field of all ChnCtrl registers |

#### Channel Abort Register (Offset 0x40)

The register controls the abortion of the DMA channel transfers, one-bit per channel. Write 1 to stop the current transfer of the corresponding channel. The abort bit is automatically cleared by hardware after triggering the channel abort event.

| Bit | R/W | Reset | Name    | Description                                         |

|-----|-----|-------|---------|-----------------------------------------------------|

| N:0 | W   | 0x0   | ChAbort | Write 1 to this field to stop the channel transfer. |

|     |     |       |         | The bits can only be set when the corresponding     |

|     |     |       |         | channels are enabled. Otherwise, the writes will    |

|     |     |       |         | be ignored for channels that are not enabled.       |

#### Channel n Control Register (Offset 0x44+n\*0x14)

| Bit   | R/W | Reset | Name         | Description                                 |

|-------|-----|-------|--------------|---------------------------------------------|

| 31:30 | R/W | NA    | Reserved     | NA                                          |

| 29    | R/W | 0x0   | Priority     | Channel priority level.                     |

|       |     |       |              | 0=lower priority                            |

|       |     |       |              | 1=higher priority                           |

| 28:25 | NA  | NA    | Reserved     | NA                                          |

| 24:22 | R/W | 0x0   | SrcBurstSize | Source burst size. This field indicates the |

www.onmicro.com.cn 30 / 181

|       |     | <u> </u> |             | nergy Application 昂瑞微                             |

|-------|-----|----------|-------------|---------------------------------------------------|

|       |     |          |             | number                                            |

|       |     |          |             | of transfers before DMA channel re-arbitration.   |

|       |     |          |             | Total byte of a burst is SrcBurstSize *           |

|       |     |          |             | SrcWidth.                                         |

|       |     |          |             | 0x0: 1 transfer                                   |

|       |     |          |             | 0x1: 2 transfers                                  |

|       |     |          |             | 0x2: 4 transfers                                  |

|       |     |          |             | 0x3: 8 transfers                                  |

|       |     |          |             | 0x4: 16 transfers                                 |

|       |     |          |             | 0x5: 32 transfers                                 |

|       |     |          |             | 0x6: 64 transfers                                 |

|       |     |          |             | 0x7: 128 transfers                                |

| 21:20 | R/W | 0x2      | SrcWidth    | Source transfer width                             |

|       |     |          |             | 0x0: byte transfer                                |

|       |     |          |             | 0x1: half-word transfer                           |

|       |     |          |             | 0x2: word transfer                                |

|       |     |          |             | 0x3: reserved, setting the field with this value  |

|       |     |          |             | triggers error exception                          |

| 19:18 | R/W | 0x2      | DstWidth    | Destination transfer width.                       |

|       |     |          |             | Both the total transfer byte and the total burst  |

|       |     |          |             | bytes should be aligned to the destination        |

|       |     |          |             | transfer width; otherwise the error event will be |

|       |     |          |             | triggered.                                        |

|       |     |          |             | For example, destination transfer width should    |

|       |     |          |             | be set as byte transfer if total transfer byte is |

|       |     |          |             | not aligned to word or half-word.                 |

|       |     |          |             | See SrcBurstSize field above for the definition   |

|       |     |          |             | of total burst byte and section 3.12 for the      |

|       |     |          |             | definition of the total transfer bytes.           |

|       |     |          |             | 0x0: byte transfer                                |

|       |     |          |             | 0x1: half-word transfer                           |

|       |     |          |             | 0x2: word transfer                                |

|       |     |          |             | 0x3: reserved, set the field as this value        |

|       |     |          |             | triggers error exception                          |

| 17    | R/W | 0x0      | SrcMode     | Source DMA handshake mode                         |

|       |     |          |             | 0=normal mode                                     |

|       |     |          |             | 1=handshake mode                                  |

| 16    | R/W | 0x0      | DstMode     | Destination DMA handshake mode                    |

|       |     |          |             | 0=normal mode                                     |

|       |     |          |             | 1=handshake mode                                  |

| 15:14 | R/W | 0x0      | SrcAddrCtrl | Source address control                            |

|       |     |          |             | 0x0: increment address                            |

|       |     |          |             | 0x1: decrement address                            |

|       |     |          | l           |                                                   |

www.onmicro.com.cn 31 / 181

| O IVI O C | ZIUX | Diuet | OOLII LOW E | nergy Application - 昂瑞微                          |

|-----------|------|-------|-------------|--------------------------------------------------|

|           |      |       |             | 0x2: fixed address                               |

|           |      |       |             | 0x3: reserved, setting the field with this value |

|           |      |       |             | triggers the error exception                     |

| 13:12     | R/W  | 0x0   | DstAddrCtrl | Destination address control                      |

|           |      |       |             | 0x0: increment address                           |

|           |      |       |             | 0x1: decrement address                           |

|           |      |       |             | 0x2: fixed address                               |

|           |      |       |             | 0x3: reserved, setting the field with this value |

|           |      |       |             | triggers the error exception                     |

| 11:8      | R/W  | 0x0   | SrcReqSel   | Source DMA request select. Select the            |

|           |      |       |             | request/ack handshake pair that the source       |

|           |      |       |             | device is connected to.                          |

| 7:4       | R/W  | 0x0   | DstReqSel   | Destination DMA request select. Select the       |

|           |      |       |             | request/ack handshake pair that the              |

|           |      |       |             | destination device is connected to.              |

| 3         | R/W  | 0x0   | IntAbtMask  | Channel abort interrupt mask.                    |

|           |      |       |             | 0=allow the abort interrupt to be triggered      |

|           |      |       |             | 1=disable the abort interrupt                    |

| 2         | R/W  | 0x0   | IntErrMask  | Channel error interrupt mask.                    |

|           |      |       |             | 0=allow the error interrupt to be triggered      |

|           |      |       |             | 1=disable the error interrupt                    |

| 1         | R/W  | 0x0   | IntTCMask   | Channel terminal count interrupt mask            |

|           |      |       |             | 0=allow the terminal count interrupt to be       |

|           |      |       |             | triggerd                                         |

|           |      |       |             | 1=disable the terminal count interrupt           |

| 0         | R/W  | 0x0   | Enable      | Channel enable bit                               |

|           |      |       |             | 0x0: disable                                     |

|           |      |       |             | 0x1: enable                                      |

|           |      |       |             |                                                  |

#### Channel n Source Address Register (Offset 0x48+n\*0x14)

|      | oname in ocaroo marroso mognetor (omocronio in one i) |       |         |                                                  |  |  |  |

|------|-------------------------------------------------------|-------|---------|--------------------------------------------------|--|--|--|

| Bit  | R/W                                                   | Reset | Name    | Description                                      |  |  |  |

| 31:0 | R/W                                                   | 0x0   | SrcAddr | Source starting address. When a transfer         |  |  |  |

|      |                                                       |       |         | completes, its value is updated to the ending    |  |  |  |

|      |                                                       |       |         | address + sizeof(SrcWidth).                      |  |  |  |

|      |                                                       |       |         | This address must be aligned to the source       |  |  |  |

|      |                                                       |       |         | transfer size; otherwise, an error event will be |  |  |  |

|      |                                                       |       |         | triggered.                                       |  |  |  |

#### Channel n Destination Address Register (Offset 0x4C+n\*0x14)

| Bit  | R/W | Reset | Name    | Description                                   |

|------|-----|-------|---------|-----------------------------------------------|

| 31:0 | R/W | 0x0   | DstAddr | Destination starting address. When a transfer |

www.onmicro.com.cn 32 / 181

|  |   | <u> </u>                          |                |

|--|---|-----------------------------------|----------------|

|  | С | completes, its value is updated   | to the ending  |

|  | a | address + sizeof(DstWidth).       |                |

|  | Т | This address must be aligned to   | o the          |

|  | d | destination transfer size; otherv | vise the error |

|  | e | event will be triggered.          |                |

#### Channel n Transfer Size Register (Offset 0x50+n\*0x14)

| Bit   | R/W | Reset | Name     | Description                                                                                                                                                                                                  |

|-------|-----|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:22 | NA  | NA    | Reserved | NA                                                                                                                                                                                                           |

| 21:0  | R/W | 0x0   | TranSize | Total transfer size from source. The total number of transferred bytes is TranSize * SrcWidth. The value is updated to zero when the DMA transfer is done.  If a channel is enabled with zero total transfer |

|       |     |       |          | size, the error event will be triggered and the transfer will be terminated.                                                                                                                                 |

#### Channel n Linked List Pointer Register:(Offset 0x54+n\*0x14)

| Bit  | R/W | Reset | Name      | Description                                       |

|------|-----|-------|-----------|---------------------------------------------------|

| 31:2 | R/W | 0x0   | LLPointer | Pointer to the next block descriptor. The pointer |

|      |     |       |           | must be word aligned.                             |

| 1:0  | NA  | NA    | Reserved  | NA                                                |

#### SSTATx address offset:SSTAT0--0x020,

#### SSTAT1--0x078, SSTAT2--0x0d0, SSTAT3--0x128

| Bit   | R/W | Reset | Name     | Description                                     |

|-------|-----|-------|----------|-------------------------------------------------|

| 63:32 | N/A | 0x0   | Reserved | Reserved                                        |

| 31:0  | RW  | 0x0   | SSTAT    | Source status information retrieved by hardware |

|       |     |       |          | from the address pointed to by the contents of  |

|       |     |       |          | the SSTATARx register.                          |

#### DSTATx address offset:DSTAT0--0x028,

#### DSTAT1--0x080, DSTAT2--0x0d8, DSTAT3--0x130

| Bit   | R/W | Reset | Name     | Description                                 |

|-------|-----|-------|----------|---------------------------------------------|

| 63:32 | N/A | 0x0   | Reserved | Reserved                                    |

| 31:0  | RW  | 0x0   | DSTAT    | Destination status information retrieved by |

|       |     |       |          | hardware from the address pointed to by the |

|       |     |       |          | contents of the DSTATARx register.          |

www.onmicro.com.cn 33 / 181

#### SSTATARx address offset:

#### SSTATAR0--0x030, SSTATAR1--0x088, SSTATAR2--0x0e0, SSTATAR3--0x138

| Bit   | R/W | Reset | Name     | Description                                          |

|-------|-----|-------|----------|------------------------------------------------------|

| 63:32 | N/A | 0x0   | Reserved | Reserved                                             |

| 31:0  | RW  | 0x0   | SSTATAR  | Pointer from where hardware can fetch the            |

|       |     |       |          | source status information, which is registered in    |

|       |     |       |          | the SSTATx register and written out to the SSTATx    |

|       |     |       |          | register location of the LLI before the start of the |

|       |     |       |          | next block.                                          |

#### DSTATARx address offset:

#### DSTATAR0--0x038, DSTATAR1--0x090, DSTATAR2--0x0e8, DSTATAR3--0x140

| Bit   | R/W | Reset | Name                                              | Description                                         |

|-------|-----|-------|---------------------------------------------------|-----------------------------------------------------|

| 63:32 | N/A | 0x0   | Reserved                                          | Reserved                                            |

| 31:0  | RW  | 0x0   | DSTATAR Pointer from where hardware can fetch the |                                                     |

|       |     |       |                                                   | destination status information, which is registered |

|       |     |       |                                                   | in the DSTATx register and written out to the       |

|       |     |       |                                                   | DSTATx register location of the LLI before the      |

|       |     |       |                                                   | start of the next block.                            |

#### CFGx address offset:CFG0--0x040, CFG1--0x098, CFG2--0x0f0, CFG3--0x148

| Bit   | R/W | Reset | Name      | Description                                   |

|-------|-----|-------|-----------|-----------------------------------------------|

| 63:47 | N/A | 0x0   | Reserved  | Reserved                                      |

| 46:43 | RW  | 0x0   | DEST_PER  | Assigns a hardware handshaking interface      |

|       |     |       |           | (0 - DMAH_NUM_HS_INT-1) to the                |

|       |     |       |           | destination of channel x if the               |

|       |     |       |           | CFGx.HS_SEL_DST field is 0; otherwise,        |

|       |     |       |           | this field is ignored.                        |

| 42:39 | RW  | 0x0   | SRC_PER   | Assigns a hardware handshaking interface      |

|       |     |       |           | (0 - DMAH_NUM_HS_INT-1) to the source         |

|       |     |       |           | of channel x if the CFGx.HS_SEL_SRC           |

|       |     |       |           | field is 0; otherwise, this field is ignored. |

| 38    | RW  | 0x0   | SS_UPD_EN | Source Status Update Enable. Source           |

|       |     |       |           | status information is fetched only from the   |

|       |     |       |           | location pointed to by the SSTATARx           |

|       |     |       |           | register, stored in the SSTATx register and   |

|       |     |       |           | written out to the SSTATx location of the LLI |

|       |     |       |           | if SS_UPD_EN is high.                         |

| 37    | RW  | 0x0   | DS_UPD_EN | Destination Status Update Enable.             |

|       |     |       |           | Destination status information is fetched     |

|       |     |       |           | only from the location pointed to by the      |

|       |     |       |           | DSTATARx register, stored in the DSTATx       |

|       |     |       |           | register and written out to the DSTATx        |

www.onmicro.com.cn 34 / 181

| 001 | Micro |

|-----|-------|

| _   |       |

| Ė   | 5 瑞微  |

|       |      |      |             | igy Application                                 |

|-------|------|------|-------------|-------------------------------------------------|

|       |      |      |             | location of the LLI if DS_UPD_EN is high.       |

| 36:34 | RW   | 0x1  | PROTCTL     | Protection Control bits used to drive the       |

|       |      |      |             | AHB HPROT[3:1] bus.                             |

| 33    | RW   | 0x0  | FIFO_MODE   | FIFO Mode Select. Determines how much           |

|       |      |      |             | space or data needs to be available in the      |

|       |      |      |             | FIFO before a burst transaction request is      |

|       |      |      |             | serviced.                                       |

|       |      |      |             | 0 = Space/data available for single AHB         |

|       |      |      |             | transfer of the specified transfer width.       |

|       |      |      |             | 1 = Data available is greater than or equal to  |

|       |      |      |             | half the FIFO depth for destination transfers   |

|       |      |      |             | and space available is greater than half the    |

|       |      |      |             | fifo depth for source transfers.                |

| 32    | RW   | 0x0  | FCMODE      | Flow Control Mode. Determines when              |

|       |      |      |             | source transaction requests are serviced        |

|       |      |      |             | when the Destination Peripheral is the flow     |

|       |      |      |             | controller.                                     |

|       |      |      |             | 0 = Source transaction requests are             |

|       |      |      |             | serviced when they occur. Data pre-fetching     |

|       |      |      |             | is enabled.                                     |

|       |      |      |             | 1 = Source transaction requests are not         |

|       |      |      |             | serviced until a destination transaction        |

|       |      |      |             | request occurs.                                 |

| 31    | RW   | 0x0  | RELOAD_DST  | Automatic Destination Reload. The DARx          |

|       |      |      |             | register can be automatically reloaded from     |

|       |      |      |             | its initial value at the end of every block for |

|       |      |      |             | multi-block transfers. A new block transfer is  |

|       |      |      |             | then initiated.                                 |

| 30    | RW   | 0x0  | RELOAD_SRC  | Automatic Source Reload. The SARx               |

|       |      |      |             | register can be automatically reloaded from     |

|       |      |      |             | its initial value at the end of every block for |

|       |      |      |             | multi-block transfers. A new block transfer is  |

|       |      |      |             | then initiated.                                 |

| 29:20 | RW   | 0x0  | MAX_ABRST   | Maximum AMBA Burst Length. Maximum              |

|       |      |      |             | AMBA burst length that is used for DMA          |

| 46    | D\A' | 0.0  | 000 110 501 | transfers on this channel.                      |

| 19    | RW   | 0x0  | SRC_HS_POL  | Source Handshaking Interface Polarity.          |

|       |      |      |             | 0 = Active high                                 |

| 40    | D\A' | 0. 0 | DOT US SS   | 1 = Active low                                  |

| 18    | RW   | 0x0  | DST_HS_POL  | Destination Handshaking Interface               |

|       |      |      |             | Polarity.                                       |

|       |      |      |             | 0 = Active high                                 |

|       |      |      |             | 1 = Active low                                  |

www.onmicro.com.cn 35 / 181

| 17:12 | N/A        | 0x0  | Reserved   | Reserved                                       |

|-------|------------|------|------------|------------------------------------------------|

| 11    | RW         | 0x1  | HS_SEL_SRC | Source Software or Hardware                    |

|       |            |      |            | Handshaking Select. This register selects      |

|       |            |      |            | which of the handshaking interfaces –          |

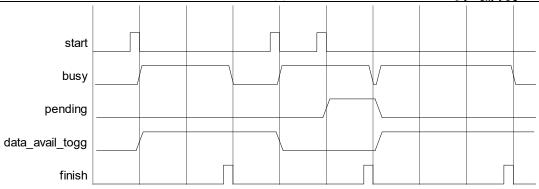

|       |            |      |            | hardware or software – is active for source    |